案例背景

隨著圖形處理需求的不斷增長,GPU的性能和效率成為了關鍵指標。傳統GPU設計復雜,成本高,且難以滿足特定應用的需求。因此,探索一種靈活、高效的GPU實現方法具有重要意義。FPGA(現場可編程門陣列)作為一種半定制集成電路,具有并行處理能力強、功耗低、體積小等優勢,成為實現GPU加速的理想選擇。

面臨的挑戰/問題

技術復雜性

GPU的架構復雜,包含多個計算單元、內存控制器、調度程序等組件,設計和實現難度較大。

FPGA資源限制

FPGA的資源有限,如何在有限的資源內實現高效的GPU加速是一個關鍵問題。

并行處理優化

GPU的并行處理能力是其高效性的關鍵,如何在FPGA上實現高效的并行處理是一個技術挑戰。

采用的策略/方法

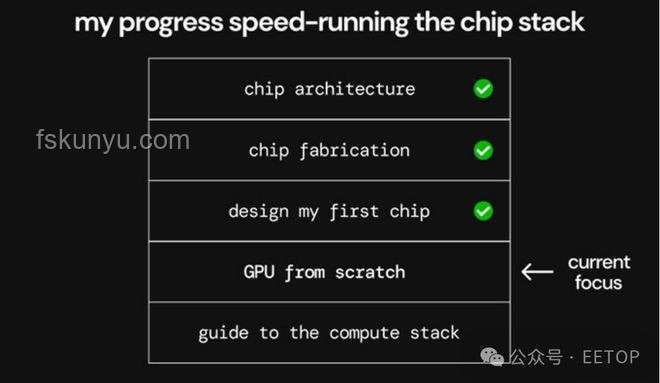

深入了解GPU架構

通過學習NVIDIA的CUDA框架和現代GPU的架構,了解GPU的核心要素,包括計算核心、內存控制器、調度程序等,為設計基于FPGA的圖形加速器奠定基礎。

利用FPGA優勢

充分利用FPGA的并行處理能力和靈活可編程性,設計高效的計算單元和內存訪問機制,實現GPU加速。

優化并行處理

采用深度流水線、并行處理方式,最大限度提高處理速度和圖像數據吞吐量,實現高效的圖形加速。

實施過程與細節

設計階段

- 架構規劃:根據GPU的核心要素,規劃基于FPGA的圖形加速器架構,包括計算單元、內存控制器、調度程序等組件。

- 資源評估:評估FPGA的資源情況,確定可用的邏輯單元、布線資源、內存等,為設計提供依據。

實現階段

- 計算單元設計:設計高效的計算單元,包括ALU(算術邏輯單元)、SFU(特殊功能單元)等,用于執行圖形處理中的計算任務。

- 內存控制器設計:設計內存控制器,管理對全局內存的訪問請求,優化內存訪問效率。

- 調度程序設計:設計調度程序,將任務分配給可用的計算單元,優化任務調度和資源利用。

- 集成與測試:將各組件集成到FPGA上,進行功能測試和性能測試,確保加速器能夠正常工作并滿足性能要求。

優化階段

- 并行處理優化:采用深度流水線、并行處理方式,提高處理速度和圖像數據吞吐量。

- 資源優化:優化FPGA資源的利用,減少不必要的資源消耗,提高加速器的效率。

- 功耗優化:通過降低工作頻率、優化計算單元的設計等方式,降低加速器的功耗。

結果與成效評估

經過實施和優化,基于FPGA的圖形加速器成功實現了GPU加速功能。性能測試結果表明,該加速器在處理圖形任務時具有較高的效率和性能。與傳統GPU相比,該加速器在特定應用場景下具有更低的功耗和更高的靈活性。

性能測試

對加速器進行了性能測試,包括處理速度、吞吐量、功耗等指標。測試結果表明,加速器在處理圖形任務時具有較高的處理速度和吞吐量,同時功耗較低。

應用場景評估

評估了加速器在特定應用場景下的表現,包括圖像處理、機器學習等領域。結果表明,加速器在這些領域具有廣泛的應用前景和潛在價值。

經驗總結與啟示

成功經驗

- 深入了解GPU架構:通過深入學習GPU的架構和運作機制,為設計基于FPGA的圖形加速器奠定了堅實基礎。

- 充分利用FPGA優勢:充分利用FPGA的并行處理能力和靈活可編程性,實現了高效的GPU加速。

- 優化并行處理:采用深度流水線、并行處理方式,提高了處理速度和圖像數據吞吐量。

失敗教訓

- 資源評估不足:在初期資源評估階段,對FPGA資源的了解不夠深入,導致在設計過程中出現了資源不足的問題。通過調整設計和優化資源利用,最終解決了這一問題。

- 測試不充分:在測試階段,對加速器的測試不夠充分,導致在后期應用中出現了一些問題。通過加強測試和調試,最終確保了加速器的穩定性和可靠性。

可推廣的啟示

- 靈活應用FPGA技術:FPGA技術具有靈活可編程性和并行處理能力,可以廣泛應用于各種領域。通過靈活應用FPGA技術,可以實現高效的硬件加速和定制化解決方案。

- 深入了解目標應用:在設計基于FPGA的硬件加速器時,需要深入了解目標應用的需求和特點,以便更好地優化設計和實現高效的加速功能。

- 加強測試與調試:在設計和實現過程中,需要加強測試和調試工作,確保加速器的穩定性和可靠性。通過充分的測試和調試,可以發現和解決潛在問題,提高加速器的質量和性能。

Q&A

Q1:基于FPGA的圖形加速器與傳統GPU相比有哪些優勢? A1:基于FPGA的圖形加速器具有靈活可編程性、低功耗和定制化解決方案等優勢。相比傳統GPU,它可以根據特定應用的需求進行優化設計,實現更高的效率和性能。 Q2:在實現過程中遇到了哪些技術難題? A2:在實現過程中遇到了資源評估不足、測試不充分等技術難題。通過調整設計和優化資源利用、加強測試和調試等方式,最終解決了這些問題并實現了高效的GPU加速功能。

文章評論 (4)

發表評論